Intel anticipa alcuni degli argomenti di discussione dell'IDF Spring 2008 di Shanghai: architettura Nehalem, bus QuickPath Interconnect, processori Dunnington, Tukwila e Larrabee e tanto altro.

Intel anticipa alcuni degli argomenti di discussione dell'IDF Spring 2008 di Shanghai: architettura Nehalem, bus QuickPath Interconnect, processori Dunnington, Tukwila e Larrabee e tanto altro.

Anticipando quello che vedremo all'IDF Spring 2008, Pat Gelsiger, Vicepresidente di Intel e Direttore Generale del Digital Enterprise Group, ha presentato le prossime novità in materia di processori:

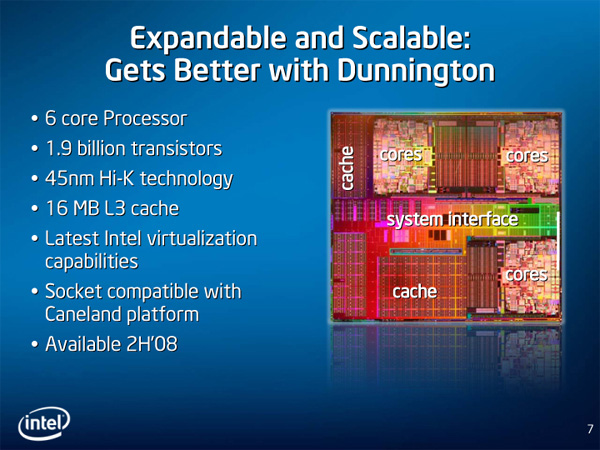

Intel Dunnington, un processore per server composto da 6 core, con un ampio quantitativo di cache e fabbricato con processo produttivo Hi-k a 45nm.

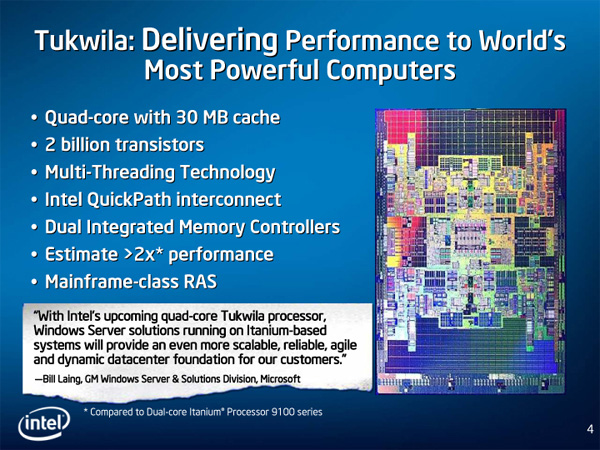

Intel Tukwila, la prossima generazione di processori Itanium, con 4 core, oltre due miliardi di transistor ed un totale di 30MB di cache! Secondo le stime del produttore dovrebbe garantire fino al doppio delle performance delle attuali CPU Itanium, anche se il TDP dovrebbe restare contenuto entro 130W.

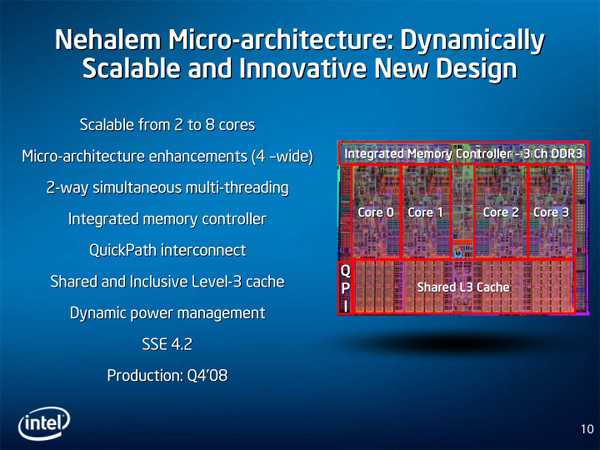

Intel Nehalem, la prossima architettura per processori desktop e notebook, permetterà di combinare da 2 ad un massimo di 8 core, per un totale di 731 milioni di transistor con fino a 8MB di cache L3. Il controller di memoria integrato permetterà di gestire moduli DDR3-800/1066/1333. Dei primi due processori Intel Nehalem per notebook, Clarksfield e Auburndale, ci siamo già occupato dettagliatamente in questa notizia, alla quale rinviamo chi voglia approfondire l'argomento.

Intel Larrabee è un processore vettoriale (VPU) di tipo SIMD (Single Instruction, Multiple Data), creato espressamente per applicazioni grafiche, ma che può gestire in maniera altrettanto efficiente anche altre applicazioni che richiedono l'elaborazione di grandi moli di dati in parallelo. Supporterà i set di API DirectX e OpenGL.

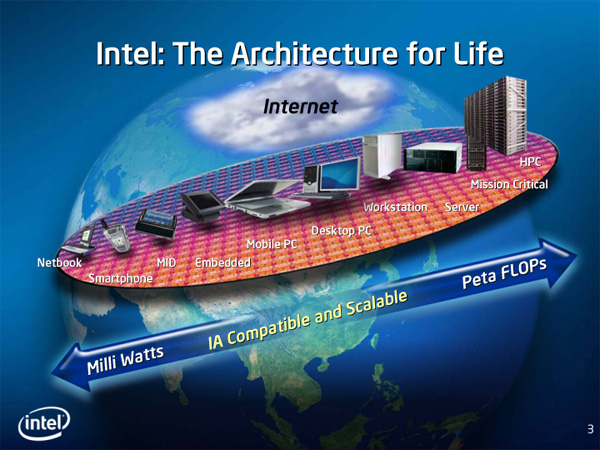

Grazie a questi nuovi microchip, la multinazionale californiana amplierà il range di prodotti basati sulla sua architettura (IA, Intel Architecture), dai server HPC agli smartphones.

Con l'introduzione della microarchitettura Intel Core, il criterio di valutazione dei processori non è più il numero di megahertz, ma la loro efficienza. Quest'anno una nuova microarchitettura, conosciuta con il nome in codice Nehalem, avrà l'obiettivo di portare efficienza, performance e scalabilità su un piano più alto.

Sotto quest'ultimo profilo, Intel Nehalem permetterà di realizzare processori ottimizzati per le applicazioni desktop, server o laptop, con estrema facilità, modulando il numero dei core, la cache, le capacità di interconnessione e di gestione della memoria. La scalabilità si tradurrà anche nella capacità di gestire dinamicamente core, cache e bus al fine di ottenere la migliore efficienza energetica.

Sul piano delle prestazioni, un ruolo di primaria importanza sarà assolto dal bus Intel QuickPath Interconnect.

Nehalem rappresenta il "tock" (nuova architettura di processore) che segue il tick (nuovo processo produttivo) nella curiosa cadenza di aggiornamento di Intel, denominata appunto "tick-tock". Pertanto, cambia l'architettura, ma non il processo produttivo, che resterà il Hi-k Metal Gate a 45nm di Intel.

Le sue caratteristiche comprenderanno:

- Multi-Threading Simultaneo (Simultaneous Multi-Threading, SMT) che permetterà di raddoppiare i thread per ciascun core;

- Supporto per tutte le istruzioni SSE4 implementate sulle CPU Penryn più sette Application Targeted Accelerators, che consentono di velocizzare specifiche applicazioni;

- Evoluzione di Intel Smart Cache con fino ad 8MB di cache L3;

- Gestione dinamica ed ottimizzata del risparmio energetico.

Merita un approfondimento quella che intel definisce "architettura QuickPath". Si tratta di un sistema costituito da due elementi:

- Controller di memoria integrato in ogni microprocessore

- Nuovo bus in grado di collegare ad alta velocità processore e componenti

Conosciuto precedentemente con il nome in codice Common System Interface (CSI), QuickPath Interconnect è un bus concorrente di AMD HyperTransport, che sostiuirà il Front Side Bus (FSB) per sfruttare tutta la potenza dei futuri processori multi-core Intel.

Con il progressivo aumento della velocità di calcolo dei processori, potrebbe verificarsi un collo di bottiglia laddove i dati non fossero resi disponibili per l'elaborazione in modo tempestivo. Diventa, così, di vitale importanza il canale tramite il quale il processore riesce ad accedere alla memoria di sistema.

Il nuovo bus metterà a disposizione tecnologie come "Scalable Shared Memory" (anche conosciuta come Non-Uniform Memory Architecture, NUMA): invece di accedere ad un'unica memoria attraverso FSB e controller, ciascun processore avrà una sua memoria dedicata alla quale potrà accedere direttamente attraverso il controller di memoria integrato. Nel caso in cui un processore avesse la necessità di accedere alla memoria dedicata ad un altro processore, potrebbe farlo attraverso il bus QuickPath Interconnect.

Il principale vantaggio di QuickPath Interconnect rispetto al vecchio FSB è nel fatto di creare una connessione punto-a-punto. Verrà così ovviato il problema che i processori debbano contendersi lo stesso canale per accedere a RAM e southbridge.

I vantaggi di QuickPath Interconnect in termini di prestazioni sono i seguenti:

- Fino a 25 GB/s di banda, circa 300 volte superiore dei bus impiegati finora;

- Architettura progettata in modo efficiente al fine di migliorare le performance;

- Caratteristiche RAS integrate (Reliability, Availability and Serviceability).