Combinando i nuovi core ARMv9 Cortex-X2, Cortex-A710 e Cortex-A510 si possono configurare CPU per ogni tipo di device, dagli indossabili ai PC. È la Total Compute CPU Solution di ARM.

Con le microarchitetture ARMv9 Mobile si completa il processo di avvicinamento di ARM al mondo dei PC. I chip ARM possono vantare un'efficienza ed una scalabilità impareggiabile ed oggi sono in grado di assicurare un livello di prestazioni assolutamente adeguato a qualsiasi computer, inclusi i PC desktop. ARM la chiama Total CPU Solution, una architettura che riesce ad assolvere alle esigenze di calcolo di qualsiasi dispositivo, dallo smartwatch ai server passando per i PC fissi e notebook.

Quella che fino a qualche anno fa era una prospettiva teorica, è adesso una realtà con Apple M1, i chromebook ARM-based e i PC Windows-on-ARM. E mentre Intel con i suoi processori X86 non riesce più a tenere il passo della legge di Moore ed ha rallentato la sua cadenza tick-tock, ARM continua a martellare presentando puntualmente ogni anno a giugno nuovi core Cortex sempre più potenti ma con consumi e profili termici sbalorditivi.

Lo schema ricalca esattamente quello dell'architettura ARM del 2020 e che oggi troviamo in tutti i processori flagship, con un gruppo di core a bassi consumi per le attività ordinarie (little core), abbinato ad un cluster di core ad alte prestazioni e, opzionalmente, ad un super-core (big core) per ottenere il massimo picco di performance in single-threading. Cortex-A55, Cortex-A78 e Cortex-x1 vengono ora sostituiti da Cortex-A510, Cortex-A710 e Cortex-X2 con miglioramenti stimati di prestazioni rispettivamente del 35%, 10% e 16% che salgono ad oltre il 100% in Machine Learning.

Architettura ARMv9

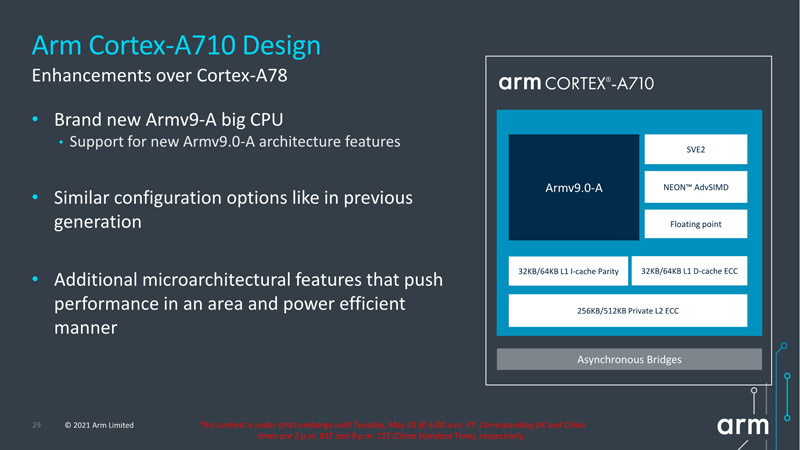

ARMv9 è il nome dell'ultima architettura ARM e rappresenta un salto generazionale significativo rispetto alla precedente v8, seppure mantenendo AArch64 come set di istruzioni base. ARM ha concentrato la sua attenzione sui profili della sicurezza, AI e DSP. Viene implementato un nuovo set di istruzioni vettoriali SVE2 che ha l'obiettivo di incrementare il parallelismo a livello dei dati tramite un approccio estremamente granulare e modulare.

Gli analisti prevedono una massiccia implementazione della AI entro il 2025 e riuscire a gestire i calcoli necessari per il Machine Learning sulla CPU potrebbe essere utile in molteplici scenari, da quelli più semplici che possono contare solo sui core Cortex a quelli più complessi dove la CPU è solo una componente di una engine eterogenea dedicata alla AI insieme a GPU Mali ed NPU Ethos.

Sul versante della sicurezza, attacchi come Spectre e Meltdown hanno evidenziato i limiti dell'attuale approccio gerarchico che permette di aggirare i privilegi di accesso delle istruzioni alla memoria. Per risolvere il problema ARM propone l'approccio Confidential Compute Architecture che prevede ambienti di esecuzione completamente isolati dall'OS e dall'hypervisor. Sono chiamati "reami" e sono gestiti da una nuova entità il "realm manager" che dovrebbe essere costituita da circa 1/10 del codice di un hypervisor.

Mentre ARM Cortex-X2 e Cortex-A710 sono una evoluzione diretta dei Cortex-X1 e Cortex-A78 con un refresh alla nuova architettura, invece i Cortex-A510 rappresentano un completo ripensamento dei core ad alta efficienza di ARM. Un re-design davvero necessario dopo anni in cui le attenzioni del chipmaker inglese si erano concentrate principalmente se non esclusivamente sui core ad alte prestazioni.

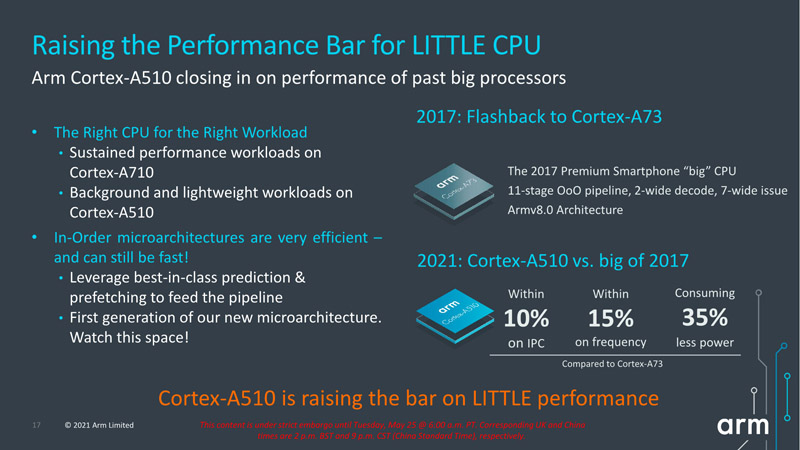

Gli ARM Cortex-A510 restano processori in-order e quindi sacrificano le prestazioni in favore di consumi particolarmente ridotti, però ARM sottolinea che questo non significa che siano lenti! Grazie a sistemi predittivi e di prefetching fra i migliori della categoria mutuati direttamente dai processori flagship del programma Cortex-X ed alla nuova architettura ARMv9.0 si riescono a superare le prestazioni degli ARM Cortex-A73, i big core del 2017 di tipo out-of-order. E non parliamo di un vantaggio di poco conto: +10% di istruzioni per ciclo di clock (IPC), +15% frequenza di clock ma consumi più bassi del 35%.

Due ARM Cortex-A510 possono essere combinati in una coppia che prende il nome di "merged core", condividendo cache L2 e le pipeline FP/NEON/SVE2 SIMD fra i due core. Non c'è un vantaggio in termini di prestazioni e peraltro è una funzione opzionale, ma potrebbe tornare utile per ridurre il footprint dei nuovi processori o per consentire di alloggiare più di 8 core perché ogni coppia di merged core occupa solo un'interfaccia sulla DSU.

È ora supportata la decodifica di tre istruzioni per ciclo (3-wide), ed è stata anche migliorata la fase di load store che utilizza due pipeline in grado di eseguire il doppio delle operazioni di load per ciclo. Ciascuna pipeline ha una ampiezza doppia per un totale di una bandwidth quadrupla rispetto ai Cortex-A55.

ARM Cortex-A710 apporta piccoli avanzamenti rispetto al già ottimo ARM Cortex-A78 come una branch prediction più accurata oltre all'architettura ARMv9. Il margine di miglioramento in termini di IPC rispetto al suo predecessore è molto risicato, ma in realtà è stato frenato da ARM riducendo da 6 a 5 (5-wide) la decodifica di istruzioni per ciclo. Il risultato è un incremento di efficienza del 30% rispetto ai Cortex-A78. L'obiettivo è quello di mantenere un bilanciamento fra prestazioni e consumi e di creare una più accentuata differenziazione rispetto al big core Cortex-X2. Se quest'ultimo è indirizzato alle performance in assoluto, il Cortex-A710 mira ad essere il campione delle performace sostenute.

Anche se probabilmente continueremo a vederli impiegati in processori ultramobile come big core come già succede ai Cortex-A78, diventa più evidente il posizionamento dei Cortex-A710 come middle core. Il ruolo di big core viene assunto in maniera più marcata dai Cortex-X2 che puntano a raggiungere le più alte prestazioni di picco sacrificando l'efficienza che, come al solito, per ARM non è soltanto il rapporto fra performance e consumi ma tiene in considerazione anche l'area del core.

I core Cortex-X2 possono essere utilizzati in SoC flagship per migliorare le prestazioni in single threading come già succede oggi per i Cortex-X1 ma ARM fa riferimento ad un altro intrigante scenario d'impiego: possono essere una perfetta piattaforma di computing per device di ampio formato come laptop e PC desktop.

I Cortex-X2 differiscono dai Cortex-A710 anche perché possono solo eseguire applicazioni AArch64 completando la transizione ai 64-bit, mentre i secondi sono gli unici core ARMv9 ancora compatibili con l'architettura a 32-bit AArch32 ed il relativo set di istruzioni.

ARM ha continuato a perfezionare la branch prediction considerata essenziale per massimizzare le prestazioni. Questa fase resta disaccoppiata da quella di fetching con tutti i conseguenti benefici in termini di prestazioni, ma il miglioramento più significativo in questa nuova generazione riguarda l'accuratezza della predizione che ha permesso di ridurre di molto il numero di errori.

Sia per i Cortex-X2 sia per i Cortex-A710, ARM è riuscita a diminuire gli stadi di smistamento da 2 ad 1, per una riduzione complessiva degli stadi della pipeline da 11 a 10. Un altro miglioramento che riguarda l'architettura out-of-order di questi core è l'incremento del 30% del ReOrder Buffer (ROB) che riorganizza i dati secondo l'ordine richiesto dal programma e permette di effettuare un rapido rollback in caso di errori di branch prediction.

DSU-110 DynamIQ Shared Unit 110

ARM DynamIQ consente un approccio modulare alla CPU permettendo di realizzare, ad esempio, configurazioni di fascia bassa con 4 core ARM Cortex-A510, di fascia media con 6 core (4 Cortex-A510 e due Cortex-A710) o di fascia alta con 4 core Cortex-a510, 3 core Cortex-a710 e 1 Cortex-X2. Astrattamente sarebbe possibile spingersi fino a configurazioni di 8 core ARM Cortex-X2. Tutti i core sono raggruppati in un unico cluster chiamato DynamIQ Shared Unit anche se spesso continuiamo ad usare impropriamente il termine "cluster" per identificare i gruppi di core che compongono la DSU (consideriamolo un retaggio dell'architettura big.LITTLE).

La nuova DynamIQ Shared Unit 110 è stata completamente riprogettata con un focus ancora più marcato su prestazioni e consumi. Sul primo versante supporta una cache L3 più ampia, fino a 16MB contro gli 8MB precedenti (anche se è un limite teorico, i SoC di categoria premium attuali si fermano a 4MB di cache L3), ed è in grado di raggiungere una bandwidth L3 fino a 5 volte superiore.

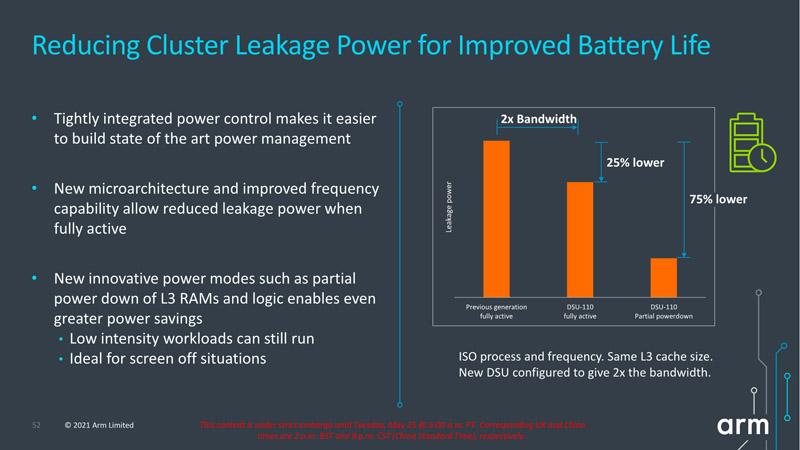

Sul versante dei consumi, la nuova DSU è più efficiente e questo significa avere un margine di vantaggio sul profilo termico che può essere utilizzato per raggiungere frequenze più alte a parità di consumi o per ridurre i consumi a parità di frequenze. ARM calcola una dispersione inferiore del 25% con una bandwidth doppia rispetto alla DSU precedente ed è stato implementato un nuovo stato di "spegnimento parziale" che consente di ridurre i consumi del 75% nelle fasi di idle.

ARM Corelink Interconnect CI-700 e NI-700

Abbiamo chiarito che le DSU si comportano come un unico cluster ma come si interconnettono vari cluster fra loro o con altre componenti del SoC come NPU Ethos e GPU Mali? Tramite un bus che però lato ultramobile/client ARM non aggiorna da diversi anni, e quindi è divenuto urgente un refresh che possa rispondere alle esigenze di un moderno sistema di heterogeneous computing o Total compute Solution in grado di supportare giochi AAA, HDR e alti framerate.

Il nuovo bus che collega i cluster della CPU si chiama CoreLink CI-700 e comprende il supporto per alcune delle più recenti novità a livello di architettura come il protocollo AMBA CHI issue E e MTE Memory Tagging Extension. Migliora anche la scalabilità con la possibilità di utilizzare da 1 ad 8 cluster con fino ad 8 controller di memoria.

In aggiunta è possibile configurare da 1 ad 8 blocchi di SLC System Level Cache da 4MB ciascuno con l'obiettivo di ridurre l'accesso alla memoria esterna con un beneficio in termini di consumi.

Fra CPU e altre componenti del SoC come GPU, NPU, acceleratori, si utilizza un bus CoreLink NI-700 Network-on-Chip che fra le sue principali novità porta il supporto per il trasferimento dei dati in pacchetti, con una semplificazione ed ottimizzazione della superficie del SoC.

In conclusione, ARM propone per il 2021-2022 una soluzione altamente modulare ed adattabile che può soddisfare un ampio ventaglio di esigenze e di dispositivi diversi, dagli smartphone di fascia media ai tablet e smartphone flagship giungendo fino ai PC. Configurando un cluster DSU-110 con il massimo delle opzioni disponibili, si otterrebbe una CPU octa-core ARM Cortex-X2 con 16MB di chache L3 e 32MB di cache SLC che, a detta di ARM sarebbe più veloce del 40% in single threading rispetto ad una CPU per notebook del 2020! Che i tempi siano finalmente maturi perché i processori ARM sui notebook diventino un fenomeno mainstream?