DSU-110 DynamIQ Shared Unit 110

ARM DynamIQ consente un approccio modulare alla CPU permettendo di realizzare, ad esempio, configurazioni di fascia bassa con 4 core ARM Cortex-A510, di fascia media con 6 core (4 Cortex-A510 e due Cortex-A710) o di fascia alta con 4 core Cortex-a510, 3 core Cortex-a710 e 1 Cortex-X2. Astrattamente sarebbe possibile spingersi fino a configurazioni di 8 core ARM Cortex-X2. Tutti i core sono raggruppati in un unico cluster chiamato DynamIQ Shared Unit anche se spesso continuiamo ad usare impropriamente il termine "cluster" per identificare i gruppi di core che compongono la DSU (consideriamolo un retaggio dell'architettura big.LITTLE).

La nuova DynamIQ Shared Unit 110 è stata completamente riprogettata con un focus ancora più marcato su prestazioni e consumi. Sul primo versante supporta una cache L3 più ampia, fino a 16MB contro gli 8MB precedenti (anche se è un limite teorico, i SoC di categoria premium attuali si fermano a 4MB di cache L3), ed è in grado di raggiungere una bandwidth L3 fino a 5 volte superiore.

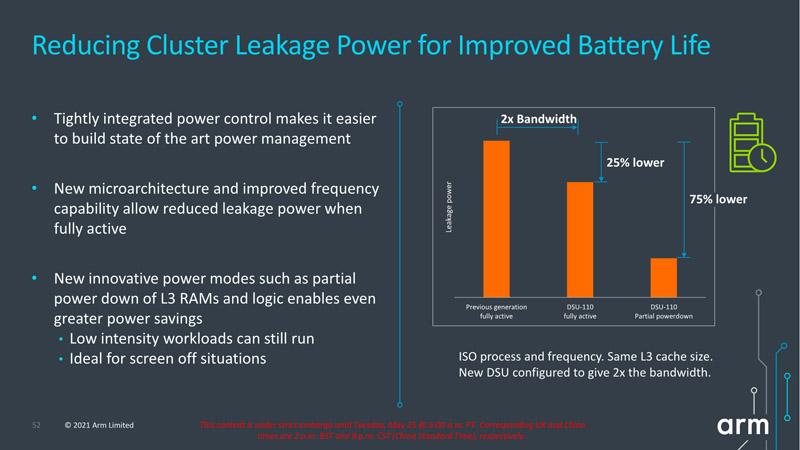

Sul versante dei consumi, la nuova DSU è più efficiente e questo significa avere un margine di vantaggio sul profilo termico che può essere utilizzato per raggiungere frequenze più alte a parità di consumi o per ridurre i consumi a parità di frequenze. ARM calcola una dispersione inferiore del 25% con una bandwidth doppia rispetto alla DSU precedente ed è stato implementato un nuovo stato di "spegnimento parziale" che consente di ridurre i consumi del 75% nelle fasi di idle.

ARM Corelink Interconnect CI-700 e NI-700

Abbiamo chiarito che le DSU si comportano come un unico cluster ma come si interconnettono vari cluster fra loro o con altre componenti del SoC come NPU Ethos e GPU Mali? Tramite un bus che però lato ultramobile/client ARM non aggiorna da diversi anni, e quindi è divenuto urgente un refresh che possa rispondere alle esigenze di un moderno sistema di heterogeneous computing o Total compute Solution in grado di supportare giochi AAA, HDR e alti framerate.

Il nuovo bus che collega i cluster della CPU si chiama CoreLink CI-700 e comprende il supporto per alcune delle più recenti novità a livello di architettura come il protocollo AMBA CHI issue E e MTE Memory Tagging Extension. Migliora anche la scalabilità con la possibilità di utilizzare da 1 ad 8 cluster con fino ad 8 controller di memoria.

In aggiunta è possibile configurare da 1 ad 8 blocchi di SLC System Level Cache da 4MB ciascuno con l'obiettivo di ridurre l'accesso alla memoria esterna con un beneficio in termini di consumi.

Fra CPU e altre componenti del SoC come GPU, NPU, acceleratori, si utilizza un bus CoreLink NI-700 Network-on-Chip che fra le sue principali novità porta il supporto per il trasferimento dei dati in pacchetti, con una semplificazione ed ottimizzazione della superficie del SoC.

In conclusione, ARM propone per il 2021-2022 una soluzione altamente modulare ed adattabile che può soddisfare un ampio ventaglio di esigenze e di dispositivi diversi, dagli smartphone di fascia media ai tablet e smartphone flagship giungendo fino ai PC. Configurando un cluster DSU-110 con il massimo delle opzioni disponibili, si otterrebbe una CPU octa-core ARM Cortex-X2 con 16MB di chache L3 e 32MB di cache SLC che, a detta di ARM sarebbe più veloce del 40% in single threading rispetto ad una CPU per notebook del 2020! Che i tempi siano finalmente maturi perché i processori ARM sui notebook diventino un fenomeno mainstream?