Tutti i dettagli sui nuovi processori Intel Alder Lake, aka Intel Core 12Gen, svelati all'Intel Architecture Day 2021: design ibrido, blocchi, Performance core Golden Cove, Efficient core Gracemont e Thread Director.

Alder Lake non è la prima CPU ibrida di Intel ma è la prima CPU di questo tipo destinata al segmento performance. Gli esperimenti precedenti di Intel erano infatti caratterizzati da bassi consumi e basse prestazioni (Intel Lakefield) e si sono conclusi con un anticipato pensionamento di queste sfortunate serie di chip.

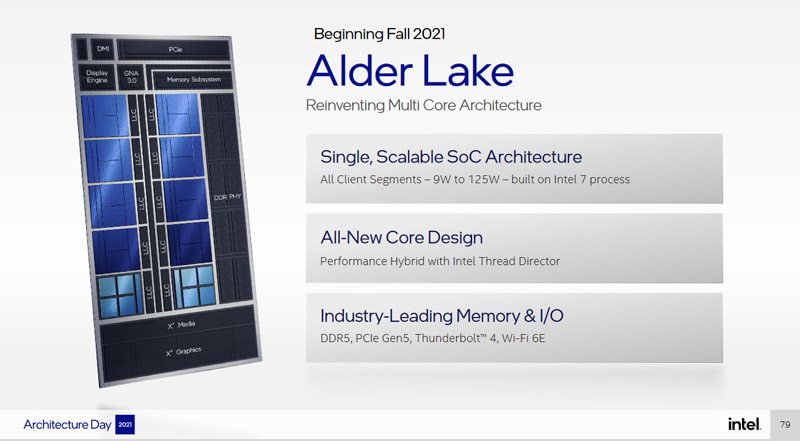

Tutt'altra sorte si augura ai nuovi Intel Alder Lake, nome in codice di quelli che saranno i processori Intel Core 12Gen e che dovrebbero invadere il mercato consumer di desktop e notebook a partire dall'ultimo trimestre del 2021. In modo simile a quanto avviene sui SoC ARM da anni, l'implementazione ibrida di Intel combina core ad alte prestazioni e core ad alta efficienza con una sostanziale differenza: Intel utilizzerà core con architettura X86.

Altra novità è che Intel Alder Lake sarà il primo processore fabbricato con processo Intel 7 che, come abbiamo spiegato nel nostro articolo di approfondimento sulla nuova nomenclatura dei nodi litografici della Casa californiana, viene considerato come equivalente ai 7nm per la densità di transistor che si riesce a raggiungere, sebbene tecnicamente sia ancora un processo a 10nm come per i Tiger Lake con l'aggiunta di una tecnologia SuperFin migliorata.

Il design ibrido di Alder Lake non permette soltanto di ottenere una migliore granularità nell'erogazione delle prestazioni, ma consente anche e soprattutto una maggiore scalabilità. Combinando diversamente core ad alte prestazioni e core ad alta efficienza si possono incontrare i bisogni di potenza e di consumi di qualsiasi segmento client, dai laptop ultrasottili ai desktop da gioco.

Intel Alder Lake: architettura ibrida e modulare

Entrando nel dettaglio della nuova architettura ibrida, i core ad alte prestazioni (Performance core o P-core) sono basati su architettura Golden Cove e sono specificamente progettati per la massima velocità, la minore latenza ed un boost di performance in single-thread. All'opposto i core ad alta efficienza (Efficiency core o E-core) sono basati su architettura Gracemont e puntano sul migliore bilanciamento di consumi e prestazioni in multi-threading.

Intel ha fornito informazioni su tre configurazioni tipo di Alder Lake (per le SKU complete bisognerà aspettare qualche settimana):

- Processore per desktop a massime prestazioni su socket LGA1700 con 8 P-core e 8 E-core;

- Processore mobile serie UP3 (corrisponde agli Intel Core U-series con TDP nel range 12-35W) ad alte prestazioni su BGA Type3 con grafica integrata Intel Xe e connettività Thunderbolt 4 con 6 P-core e 8 E-core;

- Un processore ad alta densità UP4 (corrisponde agli Intel Core Y-series con TDP massimo di 9W) su BGA Type4 per board HDI, con basso footprint (28,5 x 19 x 1,1mm) e bassi consumi composto da 2 P-core e 8 E-core.

Anandtech riporta che Intel avrebbe indicato un TDP massimo di 125W per l'intera gamma che presumibilmente corrisponde a quello delle CPU desktop. Inoltre, siccome i Performance core possono supportare l'HyperThreading mentre gli Efficiency core no, le tre configurazioni elencate raggiungono un massimo di 24, 20 e 12 thread.

Lo stesso approccio modulare viene esteso a tutti i blocchi del processore, secondo il paradigma System on a Chip. Le slide di Intel all'Architecture Day mostrano una serie di "building blocks", mattoncini da costruzione che, combinati fra loro, compongono tutte le configurazioni: oltre ai già citati core Performance ed Efficiency, possiamo elencare display engine, controller PCIe e Thunderbolt, l'acceleratore Intel GNA 3.0 dedicato all'Intelligenza Artificiale, l'Image Processing Unit, GPU Intel Xe a 32EU o 96EU, cache LLC e controller di memoria.

Ciascun blocco è a sua volta scalabile; ad esempio la cache L3 è di tipo non inclusivo e può arrivare ad un massimo di 30MB; il controller di memoria supporta overclocking, dynamic voltage-frequency scaling e tutti i più moderni standard (DDR5-4800 ed LPDDR5-5200 oltre a DDR4-3200 e LPDDR4X-4266).

Il controller PCIe può gestire 4 linee PCIe Gen 4 e fino a 16 linee PCIe Gen 5 che possono essere distribuite interamente sulla GPU in configurazione 16x, oppure ripartite fra GPU e storage in configurazione 8x+4x+4x.

Intel inoltre rafforza l'approccio SoC (System on a Chip) di Alder Lake con le tecnologie di interconnessione essenziali per permettere ai vari blocchi del processore di comunicare fra loro ("fabric"):

- Compute fabric può raggiungere i 1000GBps (o 100GBps per core o per cluster) per connettere i core della CPU e la grafica alla memoria tramite la cache di ultimo livello. Ha un alto range di frequenza dinamica e può indirizzare i dati in modo dinamico per ridurre la latenza o aumentare la bandwidth in base al carico dell'interconnessione. Può anche passare dinamicamente da una configurazione inclusiva ad una non-inclusiva per la cache di ultimo livello.

- I/O fabric è in grado di raggiungere una velocità di 64GBps adattandosi di volta in volta alla quantità di dati da trasferire.

- Memory fabric arriva ad un massimo di 204GBps anche in questo caso variando in modo dinamico ampiezza e velocità del bus a seconda che si vogliano migliorare la bandwidth, la latenza o i consumi.

Intel Thread Director

Un po' come succede sui SoC ARM, quando si vanno a combinare core di diversa natura all'interno della CPU, diventa essenziale disporre di uno scheduler evoluto che possa distribuire i thread bilanciando nel miglior modo possibile consumi e prestazioni. Questo compito è assolto dall'Intel Thread Director, un nuovo scheduler dinamico ed adattivo che riesce a valutare in tempo reale quale sia l'approccio migliore tenendo conto delle informazioni che arrivano da una telemetria hardware dello stato di ciascun core e dalla composizione di istruzioni di ciascun thread.

Ad esempio, se il microcontroller di Thread Director riconosce istruzioni complesse che richiedono alta potenza di calcolo come AVX Vector Neural Network Instructions (VNNI), il thread verrà presumibilmente indirizzato ai Performance core.

Intel Thread Director fa da tramite con lo scheduler OS, dandogli indicazioni che non solo permettono di individuare meglio il core a cui assegnare il thread ma anche di velocizzare le operazioni di scheduling. La profilazione di un thread da parte di ITD richiede solo 30 microsecondi contro i 100 microsecondi ed oltre che sarebbero necessari allo scheduler OS.

Thread Director è stato inoltre ottimizzato per Windows 11 collaborando direttamente con Microsoft e permette di trarre la massima utilità dalle nuove funzionalità del sistema operativo come la possibilità per gli sviluppatori di assegnare ai loro thread il livello EcoQoS all'interno di PowerThrottling API. I thread EcoQoS verranno indirizzati direttamente ai core ad alta efficienza.

L'altra faccia della medaglia è che questi vantaggi saranno purtroppo limitati, almeno inizialmente, a Windows 11. Windows 10 si affiderà ad una versione più semplice di Intel HGS (Hardware Guided Scheduling) mentre il supporto per Thread Director per Linux non è stato fra le priorità di Intel e potrebbe richiedere tempi lunghi per essere implementato.

L'architettura dei core ad alta efficienza, nota anche con il nome in codice Gracemont, è del tipo fuori-ordine senza SMT (Simultaneous Multithreading) e quindi non è in grado di eseguire due thread per core come fanno i core dotati di Intel HyperThreading. Si tratta dell'architettura di core più efficiente mai realizzata da Intel ed è destinata a sostenere alti volumi di multithreading e multitasking senza incidere troppo sui consumi. La scalabilità delle prestazioni rispetto alle esigenze di calcolo contingenti avviene, quindi, principalmente variando il numero di core coinvolti.

Sebbene i core Gracemont siano un'evoluzione delle architetture di core dei processori Atom, tuttavia si distaccano completamente dai loro predecessori. Tant'è vero che Intel mette a confronto i suoi nuovi Efficient core Gracemont a 10nm con i core Skylake a 14nm che sono stati alla base di moltissimi processori Intel Core negli ultimi anni (e non Intel Atom). Il risultato è un miglioramento del 40% delle performance su singolo thread a parità di consumi, o invertendo la prospettiva, una riduzione del 40% dei consumi a parità di prestazioni. Il miglioramento di efficienza sale addirittura all'80% confrontando 4 core Gracemont con 2 core Skylake (4 thread in HT) nell'esecuzione di 4 thread in simultanea.

La migliore efficienza è stata impiegata da Intel per supportare un più ampio intervallo di frequenze di clock. In questo modo gli E-core possono sia lavorare a bassi consumi, sia raggiungere frequenze di clock più alte quando devono smaltire task più impegnativi. Oltre ad un vantaggio in termini di frequenze, i nuovi E-core segnano anche l'introduzione di innovazioni volte a migliorare il volume di IPC (Istruzioni per Ciclo di clock).

Sul versante del Front-End, Intel ha implementato una branch target cache con 5000 elementi per una branch target prediction più accurata. Ha anche raddoppiato la cache istruzioni L1 portandola dai 32KB dei core Tremont a 64KB; un incremento necessario anche per supportare la nuova funzionalità di decodifica della lunghezza delle istruzioni on-demand che genera informazioni pre-decodifica che vengono proprio immagazzinate nella cache istruzioni. Un clustered decoder out-of-order permette inoltre di effettuare la decodifica di fino a 6 istruzioni per ciclo mantenendo comunque un elevato livello di efficienza.

Intel si è preoccupata di massimizzare il parallelismo per sfruttare al meglio le potenzialità dell'esecuzione fuori ordine sui nuovi core, aumentando le dimensioni della finestra di esecuzione fino a 256 elementi e portando le porte di esecuzione a 17. Con l'aggiunta di un'unità di allocazione 5-wide e di ritiro 8-wide, si riesce a migliorare di molto il volume di IPC rispetto ai core Skylake assicurando al tempo stesso consumi inferiori.

Sul versante del Back-end le 17 porte di esecuzione corrispondono a 4 pipeline per ALU per i calcoli sui numeri interi (di cui due capaci di moltiplicazioni e divisioni), 4 Address Generator Unit AGU (equamente suddivise fra load/store), 3 piepline per ALU per i calcoli vettoriali e a virgola mobile. Le restanti 6 porte sono dedicate alle diramazioni e allo store dei dati.

La cache L1 dati ammonta a 32KB e ci sono 4MB di cache L2 condivisi fra 4 E-core. Sono anche supportate le tecnologie di sicurezza Intel Control-flow Enforcement Technology e Intel Virtualization Technology Redirection. Intel ha rinnovato anche il set di istruzioni supportate (ISA) che comprende non solo AVX ma anche AVX2 (per la prima volta su una microarchitettura della famiglia Atom) e AVX2-VNNI che accelerano i calcoli per le reti neurali.

Un altro vantaggio di questi core è che hanno un basso footprint: nella stessa area di un singolo P-core, Intel riesce ad alloggiare 4 E-core ed i loro 4MD ci cache condivisa.

Golden Cove è il nome in codice della nuova architettura di core ad alte prestazioni di Intel destinata tanto ai PC (Alder Lake) quanto a server e workstation (Sapphire Rapids). Sebbene sia una evoluzione delle microarchitetture dei processori Intel Core degli ultimi anni e quindi possa essere considerata come un aggiornamento dei core Willow cove di Tiger Lake, tuttavia ci sono così tante novità che la Casa di Santa Clara considera questi core come i capostipite di una nuova generazione.

Molte di queste novità sono concentrate nel Front-End, caratterizzato da una unità di decodifica 6-wide che costituisce un'anteprima assoluta per l'architettura X86. Per alimentare il nuovo decoder più ampio è stato necessario aumentare da 16 a 32 byte il fetching delle istruzioni per ciclo, inoltre anche se la cache L1 istruzioni resta di 32KB, tuttavia è stata ridotta la latenza aumentando le dimensioni dei buffer iTLB 4K e 2M/4M (rispettivamente da 128 a 256 elementi e da 16 a 32 elementi).

Allo stesso tempo sono quasi raddoppiate anche la bandwidth e le dimensioni della cache delle micro-operazioni (μops) che diventa 8-wide e passa da 2,25K a 4K elementi. Con una cache μops con un maggiore hit rate si può migliorare velocità ed efficienza saltando la fase di decodifica. Decoder e cache μops alimentano la μops queue che viene ampliata da 70 a 72 elementi per thread ma, se non si utilizza l'HyperThreading e quindi si elabora un solo thread per core, allora quell'unico thread può contare sull'intero pool di 144 elementi.

La branch target cache passa da 5K a 12K elementi, non solo per incrementare l'accuratezza della branch prediction, ma anche per assecondare il costante incremento di dimensioni e complessità del codice delle applicazioni. L'unità di allocazione diventa 6-wide e aumenta anche la dimensione della finestra di esecuzione con un Reorder-Buffer ROB di 512 elementi ed uno scheduler più ampio.

Le porte di esecuzione passano da 10 a 12 e corrispondono nel Back-End a 5 pipeline miste in grado di elaborare calcoli sui numeri interi e sui numeri vettoriali ed a virgola mobile, a differenza di quanto accade sugli E-core che hanno porte di esecuzione separate, e 5 AGU (3 load e 2 store). 2 porte sono destinate allo store dei dati. Completa il quadro una cache L2 dedicata che sui processori client ha una capacità di 1,25MB e sulle controparti server raggiunge i 2MB ma la vera novità è un prefetcher L2 completamente ridisegnato che analizza il programma in esecuzione per predeterminare quelli che possono essere i più verosimili schemi di accesso alla memoria.

Vale la pena osservare che, pur di mantenere una omogeneità delle istruzioni fra P-core ed E-core, Intel ha disabilitato il supporto per le istruzioni AVX512 che era invece presente sui processori antecedenti. Un supporto che resta quiescente nei P-core e viene sbloccato soltanto nelle CPU per server Sapphire Rapids.

Confrontando i nuovi P-core con i core Cypress Cove dei processori desktop 11Gen Intel Core i9-11900K Rocket Lake, a frequenza ISO ed utilizzando una serie di popolari benchmark come SYSmark 25, CrossMark, PCMark 10, SPEC CPU 2017, WebXPRT 3, Geekbench 5, si stima un incremento medio delle performance del 19%.