Tutti i dettagli sui nuovi processori Intel Alder Lake, aka Intel Core 12Gen, svelati all'Intel Architecture Day 2021: design ibrido, blocchi, Performance core Golden Cove, Efficient core Gracemont e Thread Director.

Alder Lake non è la prima CPU ibrida di Intel ma è la prima CPU di questo tipo destinata al segmento performance. Gli esperimenti precedenti di Intel erano infatti caratterizzati da bassi consumi e basse prestazioni (Intel Lakefield) e si sono conclusi con un anticipato pensionamento di queste sfortunate serie di chip.

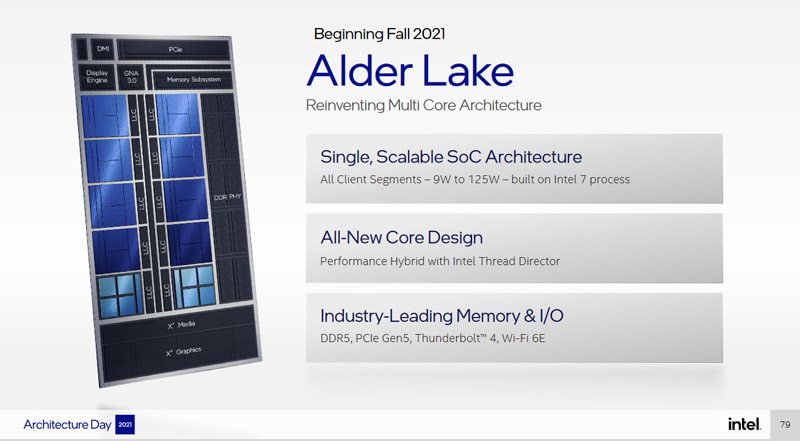

Tutt'altra sorte si augura ai nuovi Intel Alder Lake, nome in codice di quelli che saranno i processori Intel Core 12Gen e che dovrebbero invadere il mercato consumer di desktop e notebook a partire dall'ultimo trimestre del 2021. In modo simile a quanto avviene sui SoC ARM da anni, l'implementazione ibrida di Intel combina core ad alte prestazioni e core ad alta efficienza con una sostanziale differenza: Intel utilizzerà core con architettura X86.

Altra novità è che Intel Alder Lake sarà il primo processore fabbricato con processo Intel 7 che, come abbiamo spiegato nel nostro articolo di approfondimento sulla nuova nomenclatura dei nodi litografici della Casa californiana, viene considerato come equivalente ai 7nm per la densità di transistor che si riesce a raggiungere, sebbene tecnicamente sia ancora un processo a 10nm come per i Tiger Lake con l'aggiunta di una tecnologia SuperFin migliorata.

Il design ibrido di Alder Lake non permette soltanto di ottenere una migliore granularità nell'erogazione delle prestazioni, ma consente anche e soprattutto una maggiore scalabilità. Combinando diversamente core ad alte prestazioni e core ad alta efficienza si possono incontrare i bisogni di potenza e di consumi di qualsiasi segmento client, dai laptop ultrasottili ai desktop da gioco.

Intel Alder Lake: architettura ibrida e modulare

Entrando nel dettaglio della nuova architettura ibrida, i core ad alte prestazioni (Performance core o P-core) sono basati su architettura Golden Cove e sono specificamente progettati per la massima velocità, la minore latenza ed un boost di performance in single-thread. All'opposto i core ad alta efficienza (Efficiency core o E-core) sono basati su architettura Gracemont e puntano sul migliore bilanciamento di consumi e prestazioni in multi-threading.

Intel ha fornito informazioni su tre configurazioni tipo di Alder Lake (per le SKU complete bisognerà aspettare qualche settimana):

- Processore per desktop a massime prestazioni su socket LGA1700 con 8 P-core e 8 E-core;

- Processore mobile serie UP3 (corrisponde agli Intel Core U-series con TDP nel range 12-35W) ad alte prestazioni su BGA Type3 con grafica integrata Intel Xe e connettività Thunderbolt 4 con 6 P-core e 8 E-core;

- Un processore ad alta densità UP4 (corrisponde agli Intel Core Y-series con TDP massimo di 9W) su BGA Type4 per board HDI, con basso footprint (28,5 x 19 x 1,1mm) e bassi consumi composto da 2 P-core e 8 E-core.

Anandtech riporta che Intel avrebbe indicato un TDP massimo di 125W per l'intera gamma che presumibilmente corrisponde a quello delle CPU desktop. Inoltre, siccome i Performance core possono supportare l'HyperThreading mentre gli Efficiency core no, le tre configurazioni elencate raggiungono un massimo di 24, 20 e 12 thread.

Lo stesso approccio modulare viene esteso a tutti i blocchi del processore, secondo il paradigma System on a Chip. Le slide di Intel all'Architecture Day mostrano una serie di "building blocks", mattoncini da costruzione che, combinati fra loro, compongono tutte le configurazioni: oltre ai già citati core Performance ed Efficiency, possiamo elencare display engine, controller PCIe e Thunderbolt, l'acceleratore Intel GNA 3.0 dedicato all'Intelligenza Artificiale, l'Image Processing Unit, GPU Intel Xe a 32EU o 96EU, cache LLC e controller di memoria.

Ciascun blocco è a sua volta scalabile; ad esempio la cache L3 è di tipo non inclusivo e può arrivare ad un massimo di 30MB; il controller di memoria supporta overclocking, dynamic voltage-frequency scaling e tutti i più moderni standard (DDR5-4800 ed LPDDR5-5200 oltre a DDR4-3200 e LPDDR4X-4266).

Il controller PCIe può gestire 4 linee PCIe Gen 4 e fino a 16 linee PCIe Gen 5 che possono essere distribuite interamente sulla GPU in configurazione 16x, oppure ripartite fra GPU e storage in configurazione 8x+4x+4x.

Intel inoltre rafforza l'approccio SoC (System on a Chip) di Alder Lake con le tecnologie di interconnessione essenziali per permettere ai vari blocchi del processore di comunicare fra loro ("fabric"):

- Compute fabric può raggiungere i 1000GBps (o 100GBps per core o per cluster) per connettere i core della CPU e la grafica alla memoria tramite la cache di ultimo livello. Ha un alto range di frequenza dinamica e può indirizzare i dati in modo dinamico per ridurre la latenza o aumentare la bandwidth in base al carico dell'interconnessione. Può anche passare dinamicamente da una configurazione inclusiva ad una non-inclusiva per la cache di ultimo livello.

- I/O fabric è in grado di raggiungere una velocità di 64GBps adattandosi di volta in volta alla quantità di dati da trasferire.

- Memory fabric arriva ad un massimo di 204GBps anche in questo caso variando in modo dinamico ampiezza e velocità del bus a seconda che si vogliano migliorare la bandwidth, la latenza o i consumi.

Intel Thread Director

Un po' come succede sui SoC ARM, quando si vanno a combinare core di diversa natura all'interno della CPU, diventa essenziale disporre di uno scheduler evoluto che possa distribuire i thread bilanciando nel miglior modo possibile consumi e prestazioni. Questo compito è assolto dall'Intel Thread Director, un nuovo scheduler dinamico ed adattivo che riesce a valutare in tempo reale quale sia l'approccio migliore tenendo conto delle informazioni che arrivano da una telemetria hardware dello stato di ciascun core e dalla composizione di istruzioni di ciascun thread.

Ad esempio, se il microcontroller di Thread Director riconosce istruzioni complesse che richiedono alta potenza di calcolo come AVX Vector Neural Network Instructions (VNNI), il thread verrà presumibilmente indirizzato ai Performance core.

Intel Thread Director fa da tramite con lo scheduler OS, dandogli indicazioni che non solo permettono di individuare meglio il core a cui assegnare il thread ma anche di velocizzare le operazioni di scheduling. La profilazione di un thread da parte di ITD richiede solo 30 microsecondi contro i 100 microsecondi ed oltre che sarebbero necessari allo scheduler OS.

Thread Director è stato inoltre ottimizzato per Windows 11 collaborando direttamente con Microsoft e permette di trarre la massima utilità dalle nuove funzionalità del sistema operativo come la possibilità per gli sviluppatori di assegnare ai loro thread il livello EcoQoS all'interno di PowerThrottling API. I thread EcoQoS verranno indirizzati direttamente ai core ad alta efficienza.

L'altra faccia della medaglia è che questi vantaggi saranno purtroppo limitati, almeno inizialmente, a Windows 11. Windows 10 si affiderà ad una versione più semplice di Intel HGS (Hardware Guided Scheduling) mentre il supporto per Thread Director per Linux non è stato fra le priorità di Intel e potrebbe richiedere tempi lunghi per essere implementato.