Intel svela i dettagli della nuova microarchitettura Nehalem e dei primi processori Core i7 che ne faranno uso: Intel QuickPaTh Interconnect, controller di memoria integrato, cache L3 e tanto altro.

Intel svela i dettagli della nuova microarchitettura Nehalem e dei primi processori Core i7 che ne faranno uso: Intel QuickPaTh Interconnect, controller di memoria integrato, cache L3 e tanto altro.

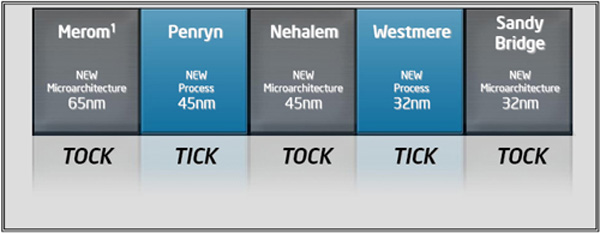

Nel Tick-Tock che scandisce il trascorrere del tempo per i processori Intel è arrivato il momento di un nuovo passo in avanti: l'ingresso della nuova microarchitettura Nehalem. Il processo produttivo resta invece fermo a 45nm, come per le precedenti CPU Penryn.

Intervallare una nuova architettura ad un nuovo processo produttivo nell'arco di sei mesi è una precisa scelta del chipmaker californiano, dopo che in passato le due cose insieme si erano rivelate un fallimento. Da allora, in un primo momento si cambia microarchitettura e poi si affina il processo produttivo.

I primi modelli di processore Nehalem raggiungeranno il mercato a Novembre, sotto il nome di Intel Core i7, e saranno dei quad-core per desktop, ma, nei progetti di Intel, Nehalem percorrerà trasversalmente ogni segmento, dai notebook ai server: sarà un'architettura scalabile, composta da un numero variabile di core (2 per i notebook, 4 per i desktop e 8 per i server) cui si aggiungeranno componenti modulari a seconda della destinazione d’uso.

Le parole chiave comuni a tutti sono performance ed efficienza energetica, cui si aggiungeranno, per i server virtualizzazione, affidabilità e scalabilità, per i desktop elaborazione grafica e sicurezza e per i notebook una migliore durata della batteria. I vantaggi di un unico core per tutte le fasce di mercato consistono in un comune set di feature e in un processo di ottimizzazione del software semplificato.

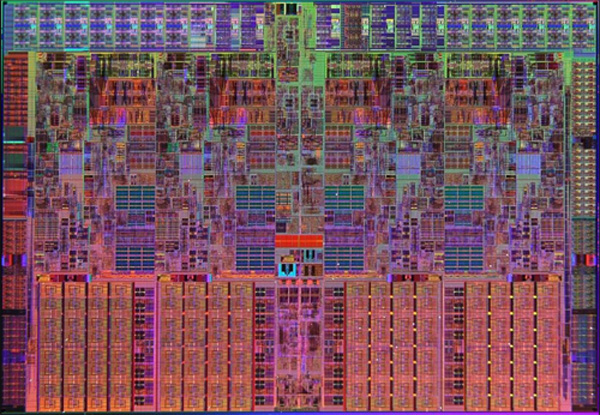

Scendendo in dettaglio nelle caratteristiche del primo processore Intel Core i7, osserviamo subito che sarà un quad-core "nativo": a differenza del passato i quattro core saranno fusi in un unico die monolitico. In sintesi, le caratteristiche delle prime CPU Intel Core i7 saranno le seguenti:

- Quad-core

- 731 milioni di transistor

- 8MB ci cache di terzo livello

- Simultaneous Multi-Threading (SMT)

- Istruzioni SSE4.2

- Controller di memoria DDR3 integrato

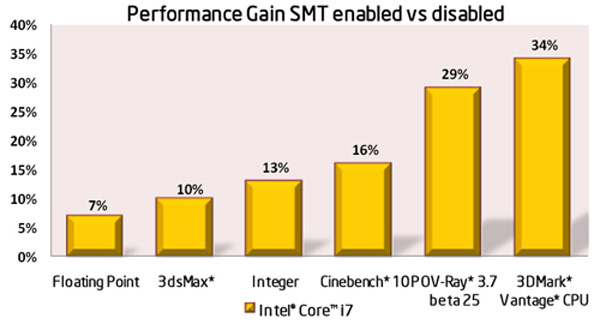

Ad uno sguardo più approfondito notiamo che cambia la struttura del processore, con l'aggiunta di 8MB di cache L3 e del controller di memoria integrato. Ritorna la capacità di eseguire due thread simultanei per ciascun core (Simultaneus Multi-Threading, anche noto come Hyper-Threading). Per cui, un Intel Core i7 quad-core sarà in grado di eseguire 8 thread in contemporanea.

Queste novità rispondono alla necessità di scalare dinamicamente le performance quando è necessario per ridurre i consumi, che costituisce il nucleo essenziale della concezione di Nehalem: performance competitive combinate con una superiore efficienza energetica.

Ciascun core Nehalem può essere suddiviso in tre aree:

- Front End (interfaccia con i dati) Si occupa della decodifica delle isruzioni e della 'Branch Prediction', letteralmente 'predizione delle diramazioni', una feature che basandosi sull'esperienza pregressa prevede l'esito di un'operazione su cui si basa l'accettazione di una istruzione di salto condizionato;

- Execution Engine (risolutore) Si occupa di pianificare ed eseguire le operazioni;

- Memory Subsystem (memoria) Dirige tutte le operazioni di caricamento e stoccaggio in memoria.

Le novità sul Front End riguardano principalmente:

- Macrofusion Un algoritmo che fonde più istruzioni trattandole come una sola per velocizzare le prestazioni e migliorare l'efficienza energetica

- Loop Stream Detector evoluto Riconosce i loop e li svolge molto + velocemente, decodificando i dati solo una prima volta.

L'Unità Logica è in grado di eseguire 6 operazioni per ciclo di clock, 3 operazioni di memoria e 3 di calcolo, ed è assistita da una Unified Reservation Station dotata di due porte in più rispetto al passato, per la pianificazione delle operazioni.

Intel Wide Dynamic Execution è,invece, un set di tecnologie che servono a consentire al processore di eseguire più istruzioni in parallelo, in modo tale da completare i task più rapidamente.

In particolare Nehalem può eseguire 4 operazioni di codifica, rinomina e di ritiro simultaneamente.

Sul fronte della Memoria, è stato incrementato il Buffer Translation Lookaside Buffer (TLB) per “rifornire” costantemente i core e non lasciarli in attesa di informazioni da elaborare. Rispetto al passato, inoltre, Nehalem disporrà di un TLB di secondo livello più veloce.

Viene introdotta la tecnologia Unaligned Cache Accesses, che garantisce la stessa velocità di esecuzione per le instruzioni allineate e non, senza andare a scapito della rapidità di esecuzione delle prime. Finora l'accesso alle istruzioni non allineate su indirizzi pari era significativamente più lento rispetto alle istruzioni allineate. Il vantaggio è tutto per gli sviluppatori che saranno liberi di utilizzare anche queste istruzioni senza temere cali di prestazioni.

Nehalem disporrà anche di Faster Synchronization Primitives. Le primitive di sincronizzazione servono a controllare le interazioni dei thread ed evitare situazioni di race condition. La nuova microarchitettura di processore si propone, quindi, di favorire le applicazioni multithreaded attraverso una minore latenza di sincornizzazione.

Restando in tema di multi-threading, un ulteriore boost prestazionale dovrebbe derivare dalla reintroduzione dell'HyperThreading. Abbandonato con l'avvento dell'architettura Intel Core perché giudicato poco determinante, HyperThreading è stato rivalutato in tempi recenti da Intel, che ne ha fatto uso dapprima sui processori per netbook Atom ed ora l'adotterà anche sulla futura generazione di CPU Nehalem. Stando alla documentazione pubblicata dalla multinazionale californiana, i benefici variano a seconda del tipo di applicazioni: in genere HyperThreading ha un apporto positivo (nel 70-80% dei casi), ma può anche essere neutro con applicazioni particolarmente ben compilate.

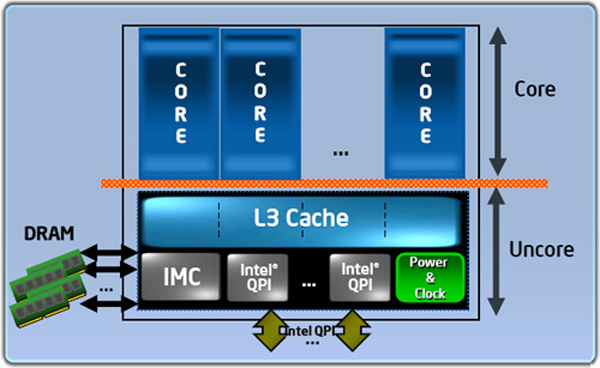

Possiamo suddividere un die di processore Nehalem in due zone:

- Core (uguale x tutte le declinazioni del prodotto)

- Uncore (modulare in funzione della macchina a cui è destinato; potrebbe anche integrare un chip grafico)

Nell'Uncore troviamo la cache L3, il controller di memoria, i controller dei link QuickPath Interconnect (QPI), un gestore di risparmio energetico, un eventuale sottosistema grafico e altro.

Nell'architettura Nehalem tutto concorre allo scopo di alimentare l'Execution Engine con un adeguato volume di dati. In quest'ottica acquista notevole importanza ridurre le latenze, aumentare banda passante e migliorare la scalabilità per poter crescere con il numero dei core per CPU.

Nehalem segna l'esordio di una nuova gerarchia di cache: alla cache L1 ed L2 si aggiunge quella L3.

- L1: la cache di primo livello saràcomposta da 32KB per le istruzioni e 32KB per i dati;

- L2: una cache di secondo livello unificata di 256KB con minore latenza (10 cicli);

- L3: la cache di terzo livello sarà unica per tutti i core e con dimensioni che dipendono dal numero di core. Per i primi processori quad-core ammonterà a 8MB.

La cache L3 ha un'altra particolarità: sarà di tipo inclusivo, o ridondante, cioé immagazzinerà le informazioni contenute nelle cache L1 e L2 di tutti i core. Si tratterebbe di una scelta focalizzata alle performance: se l'unità di calcolo necessita di informazioni che non sono presenti nella cache L1 o L2 del suo core, potrà estrarli direttamente dalla cache L3, senza dover intervenire sulle cache L1 e L2 degli altri core.

Per una maggiore efficienza e velocità, Intel ha migliorato i propri algoritmi di prefetching.

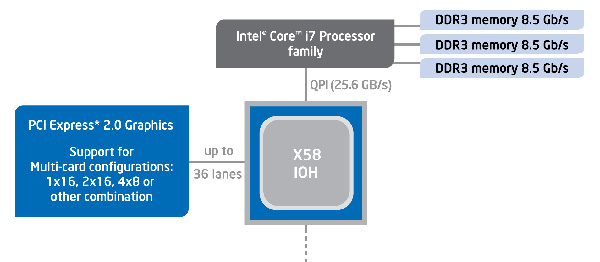

Fra le grandi innovazioni apportate da Nehalem (almeno per quanto riguarda i processori Intel) trova posto il controller di memoria integrato, anch'esso progettato avendo in mente l'obiettivo della massima scalabilità. Inizialmente i PC Intel Core i7-based avranno memorie DDR3 a 1066MHz collegate con un triplice canale. Il chipmaker di Santa Clara assicura che le latenze saranno ottime.

Considerato che ciascun processore sarà dotato di un suo controller integrato, un sistema multi-CPU assumerà l'architettura NUMA (Non Uniform Memory Access), in cui ogni processore è associato alla sua memoria (memoria locale). Se i programmi saranno ben ottimizzati, ogni processore andrà a cercare direttamente le informazioni caricate nella propria memoria con un miglioramento della latenza del 40% rispetto allo standard. Programmi generici o non ottimizzati costringeranno il processore a leggere la memoria remota, ma anche in questo caso la latenza sarà inferiore a quella delle attuali RAM.

Il Front Side Bus, FSB, per anni ha costituito la spina dorsale dei sistemi Intel based, sulla quale andavano ad innestarsi tutti gli altri bus. Era l'alveo in cui confluivano tutte le informazioni in transito fra processore, chipset e memorie. Man mano che i processori sono andati incrementando le loro prestazioni, il FSB ha aumentato la sua portata, ma non senza qualche difficoltà.

La risposta di Intel è QuickPath Interconnect, una connessione seriale point-to-point che permetterà al processore di comunicare direttamente con il controller I/O ed eventuali altri processori sul sistema, beneficiando quindi di una banda passante maggiore e di latenze sempre più ridotte.

Intel Quick Path Interconnect utilizza collegamenti bidirezionali da 6,4 GT/s, per una bandwith teorica massima di 25 GB/s per ciascun link.

Il nuovo set di istruzioni SSE4.2 consiste in acceleratori dedicati all'elaborazione di stringhe e testo, insieme ad acceleratori indirizzati a specifiche applicazioni (ATA, Application Targeted Accelerators).

Gli effetti positivi coinvolgeranno XML parsing, confronti, riconoscimento della scrittura, network storage, efficienza energetica, calcoli demografico, mappatura del genoma e altri.

I primi processori per notebook basati su architettura Nehalem saranno Auburndale, dual-core destinato ad un largo impiego su tutte le più comuni categorie di computer portatili, e Clarksfield, quad-core indirizzato a workstation e gamestation. Saranno distribuiti sul mercato a partire dalla seconda metà del 2009 e si distingueranno dai loro equivalenti desktop e server per l'assenza di Intel QuickPath Interconnect.