Memoria LLC ex L3

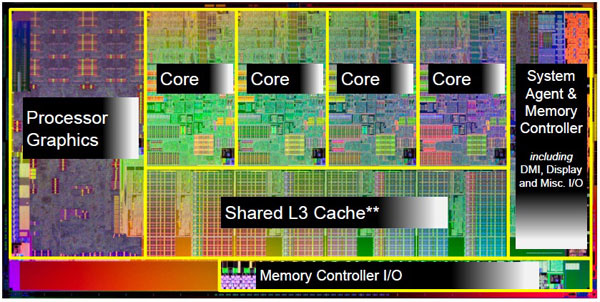

Internamente l’architettura della CPU cambia geometria: mentre nella precedente versione Nehalem-Westmere avevamo un doppio die dove uno dei due era destinato alla grafica, ora nella nuova versione Sandy Bridge abbiamo un die monolitico con i due core e il processore grafico direttamente integrati in un unico package.

Ed è all’interno di questa unica unità che troviamo il primo cambiamento nella memoria nominata cache L3.

Nella generazione passata questa memoria serviva da supporto ai core presenti, ed era esterna ad essi, completi già di cache L1 ed L2 interna. Con la nuova generazione la L3 viene rinominata in LLC (Last Level Cache), in quanto diventa una memoria generale condivisibile anche dal core grafico integrato, oltre che ovviamente dai core di calcolo presenti. Mentre prima l’L3 era costituita da un unico blocco a sé stante, ora la LLC è ripartita in numero uguale a quello dei core presenti (anche se ciascun core può accedere alla totalità della cache di terzo livello), un quad core avrà quindi una LLC divisa in quattro parti così come in un dual core sarà divisa in due parti, tutto ciò per una migliore integrazione col nuovo collegamento interno adottato da Intel e nominato Ring-Bus che unisce tutte le unità funzionali della micro-architettura, e che andremo ad analizzare meglio in seguito.

Il componente che veniva denominata uncore in Nehalem-Westmere, ora cambia denominazione in System-Agent ed integra tutti i controlli necessari al funzionamento delle comunicazioni verso l’esterno della CPU (è quella parte del processore che eredita le funzioni in precedenza svolte dal Northbridge).

Core e AVX

Come nella precedente generazione, anche in Sandy Bridge la memoria che equipaggia il processore ammonta a 64 Kbyte per la L1, e a 256 kbyte per la L2.

I cambiamenti principali apportati dagli ingegneri Intel riguardano soprattutto aspetti molto profondi del funzionamento dei core. Le istruzioni in modalità out of order (procedura con la quale una CPU esegue le istruzioni secondo un ordine di disponibilità dei dati e non nell’ordine fornito originariamente dal programma interessato) vengono ora eseguite con un front end che può ricostruire l’ordine di esecuzione delle istruzioni per velocizzare lo sfruttamento delle risorse disponibili.

Si è inoltre deciso di non utilizzare più un file di registro centralizzato RRF (Retirement Register File) ma uno fisico, chiamato PRF (Phisycal Register File), così da poter trasportare solo i riferimenti (puntatori) degli operandi al PRF insieme alle istruzioni, e non più come in passato appesantire il trasporto delle istruzioni con una copia degli operandi.

E’ grazie a questo cambiamento che è stato possibile introdurre l’AVX (Advanced Vector Extension) che, agendo su operandi a 256 bit, con un RRF avrebbe richiesto un ingigantimento dei registri e dunque un aumento dei transistor che non avrebbe giovato nè ai costi nè ai consumi.

L’ Advanced Vector Extension può essere visto come un raffinamento delle istruzioni SSE e, come detto, lavora con operandi a 256 bit, grazie a una nuova gestione nell’Execution Cluster che ha tre porte di accesso (Esecution Port): una per i dati interi e due per i dati a virgola mobile. L’espediente utilizzato dagli ingegneri per utilizzare operandi a 256 bit su strade (Data Path) a 128 bit che conducono alle 3 porte di accesso sopra citate, è stato quello di fondere 2 Data Path a 128 bit in uno solo nel momento in cui un'istruzione AVX viene chiamata, cosi da supportare senza aumento di transistor anche gli operandi a 256 bit.