Negli ultimi anni, AMD ha intensificato gli sforzi per mantenere la promessa di portare i primi computer Fusion sul mercato entro il 2011. Un po' come succede oggi per le piattaforme Danube e Nile, anche la futura ondata di portatili AMD Fusion potrà essere basata su due differenti piattaforme, denominate Sabine e Brazos, rispettivamente indirizzate ai notebook mainstream ed ai laptop ultrathin (macro-categoria nella quale il chipmaker californiano racchiude tanto i netbook quanto i notebook ultrasottili a basso voltaggio).

"Abbiamo accelerato il progetto Fusion, quindi il beneficio del know-how di ATI nell'ambito GPU al servizio di tutte quelle che sono le attività di computing e poi per l'anno prossimo in occasione del CES presenteremo le prime macchine basate sulla nuova tecnologia Fusion, che non significa avere la CPU e la GPU nello stesso die ma si tratta di avere la CPU e la GPU all'interno dello stesso silicio e quindi sfruttare al massimo le capacità di calcolo in parallelo della GPU", ci dice Sergio Ceresa.

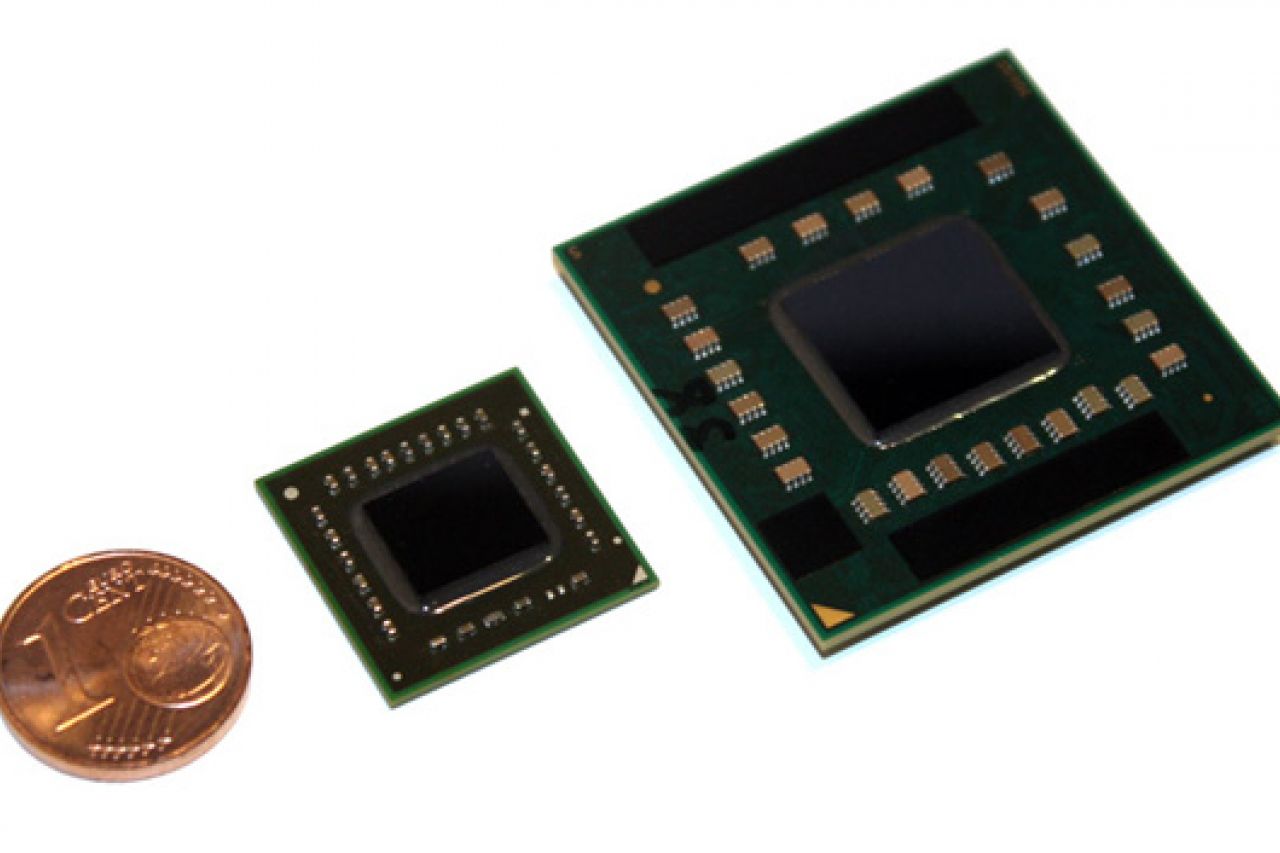

La principale differenza fra le due piattaforme consisterà nei processori impiegati, i quad-core Llano a 32nm per Sabine, ed i dual-core Ontario (TDP di 9W) e Zacate (TDP di 18W), entrambi realizzati con miniaturizzazione a 40nm, per Brazos.

Contrariamente alle attese della vigilia, sembra che la prima piattaforma ad essere rilasciata possa essere Brazos e non Sabine: "i primi ecosistemi Brazos sono già in test presso gli OEM", così come sono basate su Brazos le demo esibite da AMD all'IFA, all'IDF ed al Computex.

Ad accomunare i processori Ontario e Zacate della piattaforma Brazos sarà l'architettura su cui saranno basati i loro core, nome in codice Bobcat, e di cui ci occupiamo in modo più approfondito in questo articolo. I processori Llano, invece, saranno basati sui più potenti core Bulldozer. Ricordiamo che stiamo parlando di processori AMD Fusion, quindi di SoC (System on a Chip, o APU, Accelerated Processing Units, mella terminologia di AMD), che integrano sullo stesso die anche una GPU, un controller di memoria e altri core specializzati (come ad esempio un motore di decodifica UVD).

Premettiamo inoltre che Bobcat è una microarchitettura X86-64 con supporto per la virtualizzazione e per le istruzioni SSE, SSE2, SSE3. Quindi manca ancora il supporto per le itruzioni SSE4.1 e SSE4.2 che arriverà solo in seguito con i processori Llano ed i core Bulldozer.

Bobcat sfrutta la metodologia d'esecuzione "fuori ordine" (out of order), in base alla quale il processore può stabilire un ordine di esecuzione delle istruzioni diverso da quello impostato dal programmatore. E' un approccio comune a tutti i processori odierni con l'eccezione delle CPU Atom, per le quali Intel ha preferito adottare la modalità d'esecuzione in ordine per guadagnare un vantaggio in termini di dimesioni del die e di consumi. Ne consegue che, già sulla carta, i processori Ontario saranno sensibilmente più veloci dei loro concorrenti Pineview a parità di clock, pur mantenendo un TDP competitivo pari a soli 8W (i comuni processori Atom single-core hanno un TDP di 6,5W, mentre gli Atom N550 dual-core hanno un TDP di 8,5W).

Analizzando lo schema a blocchi di Bobcat notiamo che ciascun core ha 64KB di cache L1 parzialmente associativa (32KB per le istruzioni ed altri 32KB per i dati) e 512KB di cache di secondo livello. La Branch Prediction Unit è ancora avvolta da un alone di segretezza: AMD indica quest'area come possibile destinataria di importanti innovazioni ma non ha ancora scoperto completamente le sue carte.

Le cinque fasi originarie dell'elaborazione, Fetch (acquisizione delle istruzioni dalla memoria), Decodifica, Esecuzione, Memoria e Writeback (scrittura del risultato nel registro) vengono spezzettate in 15 stadi, permettendo di avere un livello di throughput competitivo con quello dei processori Atom (che hanno una pipeline a 16 stadi).

L'unità di decodifica a doppio binario traduce le istruzioni x86 in micro-operazioni (o micro-ops) e le trasmette agli scheduler che scandiscono il lavoro delle unità ALU, AGU ed FPU (per i calcoli in virgola mobile). In base ad informazioni divulgate da AMD, "il decoder è in grado di raggruppare l'89% delle istruzioni x86 in un'unica micro-operazione, un altro 10% in sole due micro-operazioni, ed il restante 1%, composto da istruzioni più complesse, viene tradotto in microcodice." Si tratta di un approccio efficiente, del tutto comparabile a quello implementato da Intel nei suoi processori.

Abbiamo già accennato al TDP massimo dei processori Ontario e Zacate, ma è interessante scoprire che di quei 9W e 18W, meno di 1W è consumato da ciascun core Bobcat. Questo risultato è stato ottenuto tramite un attento bilanciamento di vantaggi e costi in termini di prestazioni e consumi, privilegiando quelle soluzioni architetturali che si sono rivelate più efficienti, come i registri fisici di file, un ridotto uso delle code di scorrimento, ed una tecnica di clock gating più granulare.