Il passaggio alla realizzazione di processori basati su transistor Tri-Gate 3D, a struttura tridimensionale, diventa oggi una realtà: Paul Otellini, CEO di Intel, ha annunciato infatti che i futuri Ivy Bridge a 22 nm utilizzeranno tale rivoluzionaria soluzione.

Il passaggio alla realizzazione di processori basati su transistor Tri-Gate 3D, a struttura tridimensionale, diventa oggi una realtà: Paul Otellini, CEO di Intel, ha annunciato infatti che i futuri Ivy Bridge a 22 nm utilizzeranno tale rivoluzionaria soluzione.

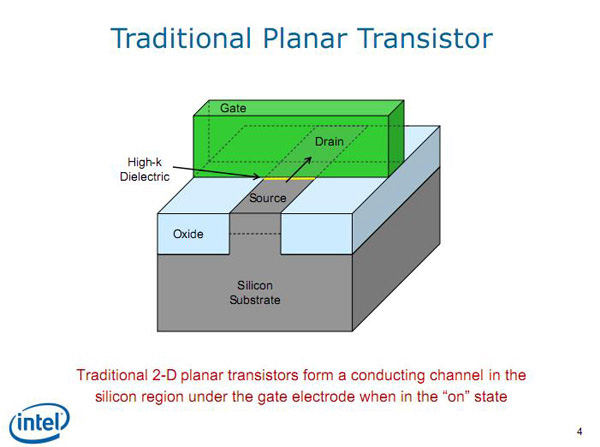

Da quando, nel 1961, venne realizzato il primo circuito integrato, che permise la miniaturizzazione dei transistor per la realizzazione di dispositivi elettronici di dimensioni contenute, molto è cambiato ma senza vere rivoluzioni. Certamente, la tecnologia ha fatto passi da gigante e i processi litografici per stampare i circuiti sui wafer di silicio hanno avuto diverse evoluzioni, sia raggiungendo miniaturizzazioni sempre più spinte sia implementando nuove tecnologie per i gate, grazie allo sviluppo di soluzioni all'avanguardia e di dielettrici più performanti.

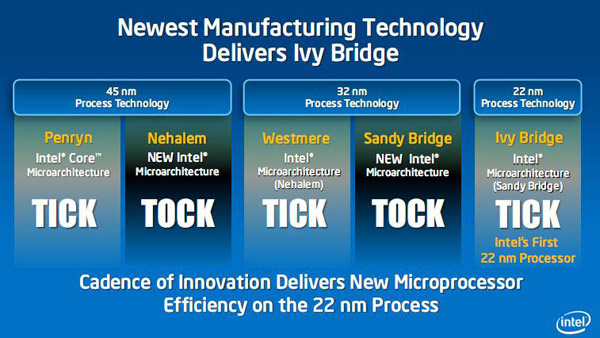

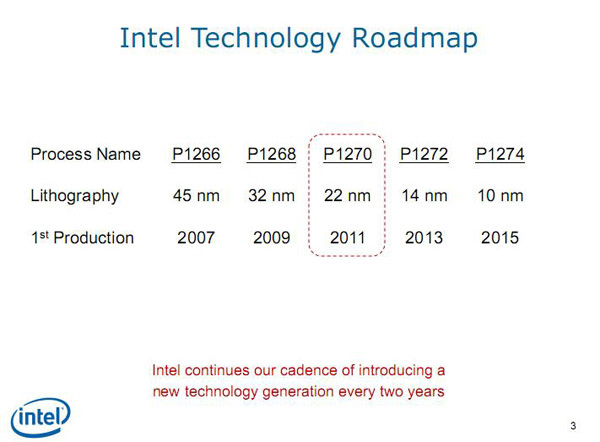

Dal 1961 a oggi ciò che non è mai cambiato è la struttura geometrica dei circuiti. Fino all'annuncio di oggi infatti i transistor erano sempre stati bidimensionali, sviluppandosi planarmente su una superficie piana. La soluzione presentata oggi, che ha del rivoluzionario, si è resa necessaria per rispettare la Legge di Moore e Intel ci ha lavorato sin dal 2002. Secondo la famosa Legge infatti, formulata nel 1965 dal cofondatore di Intel Gordon Moore, il numero di transistor in un chip avrebbe dovuto raddoppiare approssimativamente ogni anno. Questo sarebbe accaduto principalmente grazie alla loro continua miniaturizzazione, e avrebbe avuto come conseguenza la produzione di processori sempre più piccoli, economici ed energeticamente efficienti, permettendo ai chipmaker di aumentare le prestazioni e ridurre i costi ad ogni nuova generazione.

Tuttavia già dieci anni dopo, Moore fu costretto a riformulare la sua Legge, portando la previsione a un ritmo di crescita di due anni. Si poteva già intuire che il ritmo di miniaturizzazione avrebbe prima o poi raggiunto un limite dettato dalla fisica e ora quel limite è sempre più vicino. Il limite fisico attuale stimato è di 18 nm, passando alla fotolitografia tramite raggi X, si potranno forse raggiungere i 3 nm, oltre sarà impossibile scendere.

La soluzione Tri-Gate 3D permette invece di risolvere elegantemente il problema, in attesa dello sviluppo di tecnologie completamente nuove, come ad esempio i computer quantici o basati su batteri, ancora molto lontani. Ma come funziona di preciso la nuova soluzione? In pratica si è trattato di sostituire il tradizionale gate planare bidimensionale con un altro, costituito da un'aletta di silicio sottilissima, che si sviluppa quindi tridimensionalmente, elevandosi in verticale sul substrato di silicio. Per ottenere il controllo della corrente su una struttura di questo tipo però non bastava più posizionare un unico gate solo sulla parte superiore, come avveniva per i transistor biplanari.

Intel ha dovuto quindi sviluppare una soluzione nuova, che prevede la presenza di un gate su ciascuna delle tre facce dell'aletta: due su ogni lato e uno sulla parte superiore. In questo modo si riesce a controllare con grande efficienza il flusso di corrente, massimizzandolo quando il transistor è attivo e portandolo molto vicino a zero quando è inattivo, consentendogli al contempo di cambiare molto rapidamente stato, con cadute positive sulle prestazioni generali. Lo sviluppo in verticale permetterà inoltre di gestire efficacemente la densità dei chip. Anche quando si dovesse raggiungere il limite fisico per i processi di miniaturizzazione i progettisti avranno comunque la possibilità di aumentare l'altezza delle alette e in questo modo sarà quindi possibile continuare a incrementare le prestazioni e l'efficienza energetica.